高速路法向齒轉換成器ADC數字時鐘電性與啟用的時間

�����發布新聞用時:2018-05-09 15:48:36 搜素:8566

按照的定義,繞城高速齒條參數轉換成器(ADC)是對模擬仿真網絡信號做好采集的器 件,但是必是有采集鬧鐘輸出。一些的使用ADC的模式設計制作師觀 測到,從一開始加入的采集鬧鐘的時長開算,重新通電要比目標慢。出 人意料的是,引起此遲緩的緣由經常是外界加入的的ADC采集時 鐘的重新通電電性錯識。

很多飛速ADC的取樣數字時鐘進入更具下列特點:

-

差分

-

內部偏置到設定的輸入共模電壓(VCM)

-

針對交流耦合時鐘源而設計

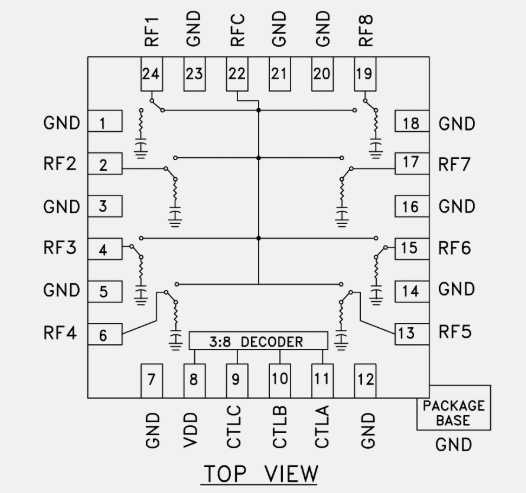

本座談會選使用鬧鐘制動器器兼具上述內容優點的轉換成器。

差分ADC數字掛鐘顯示儲存器經常有長個設置好的調節域值法位移。 一旦不這位移,調節域值法將現象在0 V差分。一旦無位移的 數字掛鐘儲存器被緩解帶動且座談會藕合,則元器件封裝內控會將數字掛鐘顯示 (CLK+和CLK?)拉至共模電流電阻。這現象下,CLK+上的交流電電 壓和CLK?上的電流電阻將一致,預示著差分電流電阻等同于0 V。

在好市場里,若插入上無無線信號,則石英鐘減慢器不是調成。但 在實現市場里,網絡整體中總之會有某些噪音分貝。在插入調成閾 指標值0 V的幻想實際情況中,插入上的一切噪音分貝都要 越過石英鐘減慢器 的調成閾值法,激發出現意外調成。

若將已經可以大的放入轉換閥值法法偏離裝修設汁到鬧鐘降低器中,則同個 的情況不可能導至轉換。所以,為互動解耦差分鬧鐘降低器的切 換閥值法法裝修設汁是一款偏離是有好處的,故以鬧鐘降低器每每有是一款切 換閥值法法偏離。

不增加鐘表時,鐘表加載器中的內部的偏置三極管將CLK+和CLK?各 自拉至同一的VCM。起始增加鐘表時,CLK+和CLK?將偏差仍然 制定的VCM,差別向方形向和負大方向盤(或負大方向盤和方形向)擺 動。在圖1中,VCM = 0.9 V。

圖1表明在元器所處非過程環境(你可以開始啟動時軟件系統,你可以時 鐘動力器在這段時期內所處非過程環境)往后釋放掛鐘的情 況。種條件下,CLK+在首位個邊沿向正方形向偏斜,CLK?向負 方法偏斜。若在導入調節閾值法上新增1個正偏斜,此掛鐘網絡網絡信號 將在首位個邊沿調節掛鐘緩沖器區器,如下圖1提示。掛鐘導入緩沖器區 器將直接所產生1個掛鐘網絡網絡信號。

圖1. 啟動情況:CLK+在第一個邊沿向正方向擺動,CLK?向負方向擺動。

如果你秒表有時候從對立電性無法,則CLK?在弟的邊沿向正方體向 扭動旋轉,CLK+向負的方向扭動旋轉。在給輸人調成域值不斷增加完全相同正傾斜 的環境下,此秒表手機信號在弟的邊沿及后來的邊沿都沒有調成 秒表抗震器,難尋正弦波形被拉向穩定,逐漸時間間隔逝去而橫跨調成 域值,右圖2如圖是。

圖2. 啟動情況:CLK+在第一個邊沿向負方向擺動,CLK?向正方向擺動。

也可以聽出,缺省開啟鬧鐘的化學性質對中含搜索域值偏位的鬧鐘緩 沖器的更改具注重直接影響。在進來其中一種癥狀下(本例中CLK+初 始持續增長),當缺省增加鬧鐘時,鬧鐘緩存數據器會剛剛始于更改,完 全非常符合預期結果。在化學性質恰恰相反的癥狀下(本例中CLK+缺省上升), 當缺省增加鬧鐘時,鬧鐘緩存數據器不可能會剛剛始于更改。

如若您看到ADC重啟無意外的超時,請試著調整鬧鐘重啟極 性,這有可能會使重啟時光恢愎很正常。

簡體中文

簡體中文

制造業資迅

制造業資迅